ハードディスク、光ディスクの信号処理で広く利用されている、PRML(Partial Response Maximum Likelihood)方式用 Radix-16ビタビ検出器(Viterbi Detector)です。 弊社独自のACS方式、パスメモリ方式をベースにしたアーキテクチャを採用しており、低面積・低レイテンシ化を同時に実現しています。

PDFはこちら

概要

低面積版と高速版の選択、軟判定出力(Soft-Output)の有無により、4種類の製品があります。

| 製品番号 | タイプ | 軟判定出力 |

|---|---|---|

| Si2540 | 低面積版 | なし |

| Si2540-H | 高速版 | なし |

| Si2540-S | 低面積版 | あり |

| Si2540-HS | 高速版 | あり |

特徴

・ 高速化のためにACSループの負荷を軽減

・ Radix-16

・ 状態数:8

・ 任意の伝達関数を設定可能

ビタビ検出器IP(Viterbi Detector)[Radix-16,SOVA対応]

・ トレースバック量を指定可能

・ 軟判定出力(Soft-Output)に対応可能

・ 低面積版、高速版の選択可能

・ 低レイテンシ

・ シングルクロック完全同期式回路

・ FPGAで動作確認後、すぐにASIC化可能

提供形態

・ Verilog RTLソースコード

・ FPGAネットリスト(Xilinx, Altera, Lattice など)

・ ASICネットリスト(お客様ご提示ライブラリにて合成)

・ CPU/DSPソースコード(C言語、アセンブラ)特にTI製DSPは経験豊富です

テストベンチ、入出力パターンとともにご提供いたします。

回路規模・性能

TSMC 65nmLP での合成例

| 製品番号 | Si2540 | Si2540-H |

|---|---|---|

| ゲート数 | 206Kgate | 285Kgate |

| 動作周波数 | 500MHz | 555MHz |

| レイテンシ | 56sample | 64sample |

| 復号速度 | 2Gbps | 2.2Gbps |

実績

・ ASIC採用実績あり

インターフェース

入力

| 信号名 | 説明 |

|---|---|

| ICLK | クロック |

| IXRST | 非同期リセット |

| IDATA0[n-1:0] | 入力データ(時刻 t) |

| IDATA1[n-1:0] | 入力データ(時刻 t-1) |

| IDATA2[n-1:0] | 入力データ(時刻 t-2) |

| IDATA3[n-1:0] | 入力データ(時刻 t-3) |

| IPR_A[m-1:0] | 伝達関数係数A |

| IPR_B[m-1:0] | 伝達関数係数B |

| IPR_C[m-1:0] | 伝達関数係数C |

| IPR_D[m-1:0] | 伝達関数係数D |

*1:Si2540-S、Si2540-HS のみ

出力

| 信号名 | 説明 |

|---|---|

| ODATA[3:0] | 検出結果 |

| OSDATA0[s-1:0] | 軟判定出力(時刻 t)(*1) |

| OSDATA1[s-1:0] | 軟判定出力(時刻 t-1)(*1) |

| OSDATA2[s-1:0] | 軟判定出力(時刻 t-2)(*1) |

| OSDATA3[s-1:0] | 軟判定出力(時刻 t-3)(*1) |

応用分野

ハードディスク、光ディスク

カスタマイズ

・ Radixの変更(Radix-2, Radix-4, Radix-8 など)

・ 状態数の変更(4状態、16状態など)

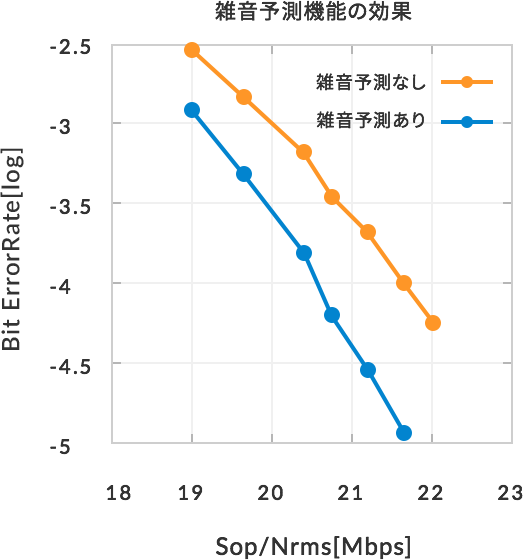

・ 雑音予測機能の追加(下図参照)

・ 信号歪み補正機能追加

軟判定ビタビ復号器IPコアに関する技術詳細、最新情報、カスタマイズのご要望など、お問い合わせは 弊社担当者 までご連絡ください。※記載内容は改良などのため予告なく変更することがあります。